void SetSysClock(void)

{

__IO uint32_t StartUpCounter = 0;

__IO uint32_t HSEStatus = 0;

__IO uint32_t HSIStartUpCounter = 0;

__IO uint32_t HSIStatus = 0;

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

// RCC->CR |= ((uint32_t)RCC_CR_HSEON); // Enable HSE

// /* Wait till HSE is ready and if Time out is reached exit */

do

// {

// HSEStatus = RCC->CR & RCC_CR_HSERDY;

// StartUpCounter++;

// } while ((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

// if ((RCC->CR & RCC_CR_HSERDY) != RESET)

// {

// HSEStatus = (uint32_t)0x01;

// }

// else

// {

// HSEStatus = (uint32_t)0x00;

// }

// if (HSEStatus == (uint32_t)0x01)

// {

// FLASH->ACR |= FLASH_ACR_ACC64; // Enable 64-bit access

// FLASH->ACR |= FLASH_ACR_PRFTEN; // Enable Prefetch Buffer

// FLASH->ACR |= FLASH_ACR_LATENCY; // Flash 1 wait state

// RCC->APB1ENR |= RCC_APB1ENR_PWREN; // Power enable

// PWR->CR = PWR_CR_VOS_0; // Select the Voltage Range 1 (1.8 V)

// while((PWR->CSR & PWR_CSR_VOSF) != RESET) // Wait Until the Voltage Regulator is ready

// {

// }

// RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; // HCLK = SYSCLK /1

// RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1; // PCLK2 = HCLK /1

// RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1; // PCLK1 = HCLK /1

// /* PLL configuration */

// RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMUL | RCC_CFGR_PLLDIV));

// RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMUL12 | RCC_CFGR_PLLDIV3);

// RCC->CR |= RCC_CR_PLLON; // Enable PLL

// while((RCC->CR & RCC_CR_PLLRDY) == 0) // Wait till PLL is ready

// {

// }

// /* Select PLL as system clock source */

// RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

// RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

// while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL) // Wait till PLL is used as system clock source

// {

// }

// }

// else // HSE startup fail, then use HSI as system clock source

// {

RCC->CR |= RCC_CR_HSION; // enable HSI as system clock source

do

{

HSIStatus = RCC->CR & RCC_CR_HSIRDY;

HSIStartUpCounter++;

} while ((HSIStatus == 0) && (HSIStartUpCounter != HSI_STARTUP_TIMEOUT)); // Wait till HSI is ready and if Time out is reached exit

if ((RCC->CR & RCC_CR_HSIRDY) != RESET)

{

HSIStatus = (uint32_t)0x01;

}

else

{

HSIStatus = (uint32_t)0x00;

}

if (HSIStatus == (uint32_t)0x01)

{

FLASH->ACR |= FLASH_ACR_ACC64; // Enable 64-bit access

FLASH->ACR |= FLASH_ACR_PRFTEN; // Enable Prefetch Buffer

FLASH->ACR |= FLASH_ACR_LATENCY; // Flash 1 wait state

RCC->APB1ENR |= RCC_APB1ENR_PWREN; // Power enable

PWR->CR = PWR_CR_VOS_0; // Select the Voltage Range 1 (1.8 V)

while((PWR->CSR & PWR_CSR_VOSF) != RESET) // Wait Until the Voltage Regulator is ready

{

}

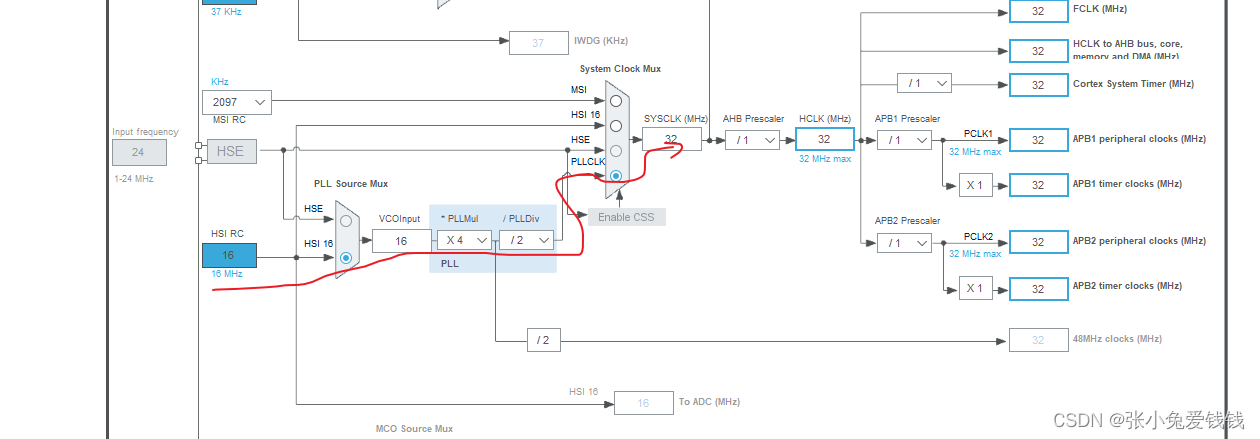

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1; // HCLK = SYSCLK /1

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1; // PCLK2 = HCLK /1

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV1; // PCLK1 = HCLK /1

/* PLL configuration */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLMUL | RCC_CFGR_PLLDIV));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSI | RCC_CFGR_PLLMUL4 | RCC_CFGR_PLLDIV2);

RCC->CR |= RCC_CR_PLLON; // Enable PLL

while((RCC->CR & RCC_CR_PLLRDY) == 0) // Wait till PLL is ready

{

}

/* Select PLL as system clock source */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)RCC_CFGR_SWS_PLL) // Wait till PLL is used as system clock source

{

}

}

else

{

// HSI startup fail

}

// }

}